Solution for design a 4bits combinational circuit 2 s complementer the output generates the 2 s complement of the input binary number.

Design a combinational circuit that generates output as 1.

For example if the input is octal digit 2 i e in binary 010.

Design a four bit combinational circuit 2 s complementer.

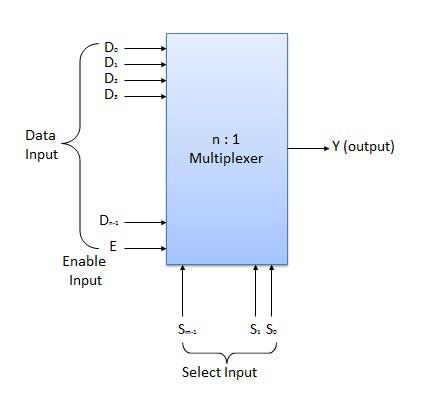

The output of combinational circuit at any instant of time depends only on the levels present at input terminals.

Eg 2 10 3 10 5 10 7 10.

The answer of prem sobel is good.

You can of course realize these independently as functions of the 3 inp.

The output generates the 2 s complement of the input binary number show that the circuit can be constructed with exclusive or gates.

A parity generator is a combinational logic circuit that generates the parity bit in the transmitter.

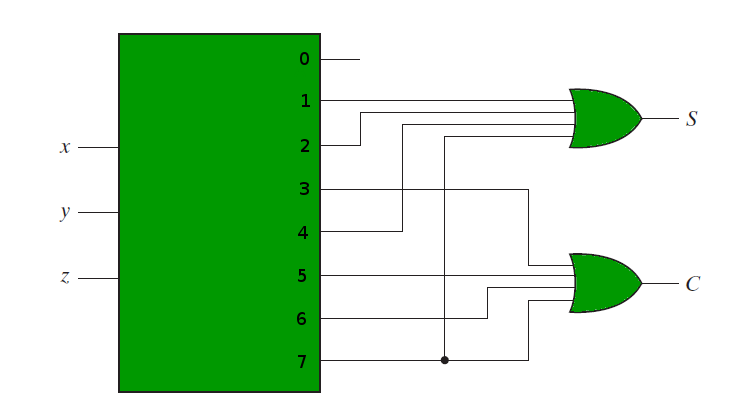

Consider the three bit number a 2 a 1 and a 0 and generate the six bit binary number s 5 s4 s3 s2 s1 and s 0 output equal to the square of the input number the block diagram of this combinational circuit is given below.

Design a circuit that has a 3 bit binary input and a single output that output 1 if it is a prime number.

On the other hand a circuit that checks the parity in the receiver is called parity checker.

The combinational circuit do not use any memory.

Compare two 1 bit numbers.

The previous state of input does not have any effect on the present state of the circuit.

Example of combinational logic circuit.

Follow the above listed points to design the logic diagram as per the given statement.

A combined circuit or devices of parity generators and parity checkers are commonly used in digital systems to detect the single bit errors in the.

The generated parity bit would be 1.

Draw the truth table for a combinational circuit that generates output as 1 only for particular input pattern double the student s vtu number 14974 write the boolean expression in standard sop form design nand nand implementation nor nor implementation for that expression derived from i design a data selector circuit for that truth.

Design a combinational logic circuit with three input variables such that it will produce logic 1 output when one or two the input variables are logic 1 but not all the three.

The output would generate the even parity bit for the corresponding input given.

Since the square of 7 the highest possible number with 3 bits is 49 and this is bigger than 2 5 you would need to have 6 output functions.